Provided for non-commercial research and education use. Not for reproduction, distribution or commercial use.

Volume 604, Issues 1-2

June 1, 2009

ISSN 0168-9002

# NUCLEAR INSTRUMENTS & METHODS IN PHYSICS RESEARCH

Section A: accelerators, spectrometers, detectors and associated equipment

Editors:

William Barletta (Coordinating Editor) Robert Klanner Fulvio Parmigiani Fabio Sauli David Wehe

Founding Editor - Kai Siegbahn

PSD8

Proceedings of the 8th International Conference on Position Sensitive Detectors Glasgow, Scotland, UK, September 1–5, 2008

http://www.elsevier.com/locate/NIMA

This article appeared in a journal published by Elsevier. The attached copy is furnished to the author for internal non-commercial research and education use, including for instruction at the authors institution and sharing with colleagues.

Other uses, including reproduction and distribution, or selling or licensing copies, or posting to personal, institutional or third party websites are prohibited.

In most cases authors are permitted to post their version of the article (e.g. in Word or Tex form) to their personal website or institutional repository. Authors requiring further information regarding Elsevier's archiving and manuscript policies are encouraged to visit:

http://www.elsevier.com/copyright

# **Author's personal copy**

Nuclear Instruments and Methods in Physics Research A 604 (2009) 23-25

Contents lists available at ScienceDirect

# Nuclear Instruments and Methods in Physics Research A

journal homepage: www.elsevier.com/locate/nima

# GASTONE: A new ASIC for the cylindrical GEM inner tracker of KLOE experiment at DAFNE

A. Balla<sup>b</sup>, G. Bencivenni<sup>b</sup>, M. Beretta<sup>b</sup>, S. Cerioni<sup>b</sup>, P. Ciambrone<sup>b</sup>, E. De Lucia<sup>b</sup>, G. De Robertis<sup>a</sup>, D. Domenici<sup>b</sup>, G. Felici<sup>b</sup>, M. Flammia<sup>b</sup>, M. Gatta<sup>b</sup>, M. Jacewicz<sup>b</sup>, R. Liuzzi<sup>a</sup>, F. Loddo<sup>a,\*</sup>, L. Monno<sup>a</sup>, M. Pistilli<sup>b</sup>, A. Ranieri<sup>a</sup>, A. Rizzi<sup>b</sup>

## ARTICLE INFO

Available online 5 February 2009

Keywords: ASIC GEM CMOS

#### ABSTRACT

GEM Amplifier Shaper Tracking ON Events (GASTONE) is a low-noise low-power mixed analog-digital ASIC designed to host 64 channels to readout the GEM inner tracker (IT) detector foreseen in the upgrade of the KLOE apparatus at the LNF e<sup>+</sup>e<sup>-</sup> DAFNE collider. Each channel is made of a charge sensitive preamplifier, a shaper, a discriminator and a monostable. Digital output data are transmitted via serial interface at 100 Mbit/s data rate. The chip has been developed by using the AMS CMOS 0.35 process. A 16 channels prototype has been produced and used to instrument the single layer IT prototype that has been tested with cosmic muons and a proton beam test at CERN.

© 2009 Elsevier B.V. All rights reserved.

# 1. Introduction

The KLOE apparatus has been designed for the study of CP symmetry violation in K<sub>L</sub> decays and, in particular, for the measurement of  $\Re(\varepsilon'/\varepsilon)$  with an accuracy of  $\sim 1 \times 10^{-4}$ . It consists of three main parts: a large cylindrical Drift Chamber (DC), a hermetic lead-scintillating fibres electromagnetic calorimeter and a large magnet surrounding the whole detector, consisting of a superconducting coil and an iron yoke. During the six-year data, KLOE has shown to be a very reliable and efficient apparatus, therefore the upgrades will be limited to some critical points. The major upgrade concerns the introduction of an inner tracker (IT) located between the beam-pipe and the DC [1]. The upgrade would allow the apparatus to reduce the 28 cm DC first hit detection, improving  $K_{0S}$ ,  $K_{0L}$  and  $K^{\pm}$  measurement near the interaction point and increasing the geometrical efficiency for  $K_{0S}$ and  $\eta$  low momentum tracks decays. The IT main requirements are a good spatial resolution ( $\sigma_{r\phi} \cong 200 \,\mu\text{m}$  and  $\sigma_z \cong 500 \,\mu\text{m}$ ) and a very low material budget in the active area (less than 2% of  $X_0$ ).

Therefore, we propose a very low mass and dead-zone-free detector based on cylindrical and dead-zone-free triple GEM technology. The tracker will be made of five concentric cylinder triple-GEM detectors instrumented with stereo strips readout for a total amount of about 35,000 readout channels. A prototype of the innermost layer is shown in Fig. 1.

Unfortunately, as a consequence of the stereo readout and the assembling procedure, the strips parasitic capacitance will range between 1 and 50 pF according to the strip position, making impossible the S/N optimization by means of capacitive matching.

Other constraints for the electronics come from the low charge amplification and gain spread of GEM devices and the quite high density readout. As a consequence high modularity, serial output and low power dissipation devices are required to instrument the detector.

# 2. Circuit description

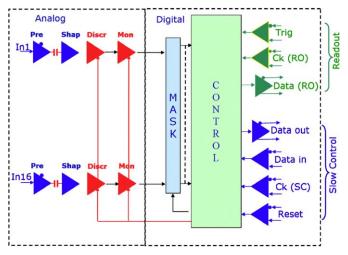

A 16-channel prototype front-end chip has been developed in the AMS CMOS 0.35  $\mu$ m process (C35B4C3) to fulfill the requirements. Its block diagram is shown in Fig. 2. The analog channel architecture is made of four different blocks: a charge sensitive preamplifier, a shaping stage, a leading-edge discriminator with programmable threshold and a monostable circuit [2,3]. The charge sensitive preamplifier integrates the input current signal, while the amplifier shaper provides noise filtering and semigaussian shaping. The discriminator generates the digital tracking information and, finally, the monostable stretches the digital signal to store the information waiting for Lev1 trigger signal.

The expected event rate on the most internal layer strip of the final detector will not be greater than 30 kHz/strip, thus a DC baseline restoration circuit to limit baseline fluctuation is not strictly needed.

<sup>&</sup>lt;sup>a</sup> INFN Sezione di Bari, Via Orabona 4, 70125 Bari, Italy

<sup>&</sup>lt;sup>b</sup> INFN Laboratori Nazionali Frascati, Via Fermi 40, 00044 Frascati (RM), Italy

<sup>\*</sup> Corresponding author. Tel.: +39 080 5442447; fax: +39 080 5442447. E-mail address: flavio.loddo@ba.infn.it (F. Loddo).

Fig. 1. Prototype of innermost layer.

Fig. 2. Circuit block diagram.

The digital section implements the control logic for threshold sensing/setting and for the serialization of the discriminated signals for data readout.

# 2.1. The analog section

The input charge amplifier consists of a common-source amplifier in cascode configuration with an active feedback made of a 150 fF capacitor and a PMOS transistor with W/L=2.5/100 and equivalent resistance of about  $100\,\mathrm{M}\Omega$  for the nominal bias current of  $100\,\mathrm{n}A$ .

The main characteristics of preamp are a gain of  $5.6\,\text{mV/fC}$  at CIN = 0 pF, a non-linearity less than 1% (0–50 fC) and a supply current of about 110  $\mu$ A.

The shaper too consists of a cascoded common source amplifier, featuring a voltage gain of 4 and non-linearity less than 3% with a supply current of about  $100\,\mu\text{A}$ . The measured peaking time is between 10 and 70 ns for a capacitive load ranging between 10 and 50 pF. The entire preamp-shaper circuit has a global charge sensitivity of about  $20\,\text{mV/fC}$ . A leading edge discriminator follows the shaper stage, with a threshold varying between 0 and more than  $200\,\text{fC}$ , with a supply current of  $180\,\mu\text{A}$ . It is characterized by a threshold spread better than 2% with an offset of about  $2.2\,\text{mV}\,\text{rms}$  over the entire threshold range. A monostable follows the discriminator stage allowing a variable output pulse ranging between  $200\,\text{ns}$  and  $1\,\mu\text{s}$ , but eventually this range could be increased tuning an external resistor. The total power consumption of the analog channel is  $1\,\text{mW}$ .

# 2.2. The digital section

The digital section of the chip has been designed and implemented to manage the 64 channels of the final chip.

Upon the arrival of the trigger signal, the discriminated signals are stored into a 96-bit register. The event frame is described in Table 1.

A relevant feature is that the 50 MHz readout clock is active only after the arriving of trigger signal, avoiding possible crosstalk with the analog section. Nevertheless, separate analog and digital power supplies have been used while all the I/O signals are implemented in the LVDS standard. At the nominal clock frequency (50 MHz), the readout of the output frame lasts 960 ns as the readout circuit uses both edge of the clock signal.

The Slow Control section of the chip is implemented in the SPI standard and consists of 28 8-bit registers, listed in Table 2, for configuring the chip functionalities, setting the threshold DACs and reading back ADCs. The SPI clock runs at 1 MHz. An internal pulsing procedure has been implemented to inject a fixed charge of 10 fC for calibration and test purpose. The chip also produces a global OR signal to be eventually used in self-triggering applications.

The digital power is about 33 mW and is predominantly due to the LVDS output drivers.

**Table 1** Event frame description.

| # Bits        | Content         |  |

|---------------|-----------------|--|

| 8 bits        | Synchronization |  |

| 2 bits        | Header          |  |

| 5 bits        | Trigger ID      |  |

| 9 bits        | Chip ID         |  |

| 64 bits       | DATA            |  |

| 8 bits at '0' | End of frame    |  |

**Table 2**List of SPI registers.

| # Registers | Content                         |

|-------------|---------------------------------|

| 8           | Mask                            |

| 4           | Threshold (1 per 16 channels)   |

| 1           | Pulse width (1 per 64 channels) |

| 5           | Read back from 5 ADCs           |

| 1           | Test pulse configuration        |

| 8           | Test pulse result               |

| 1           | Control register                |

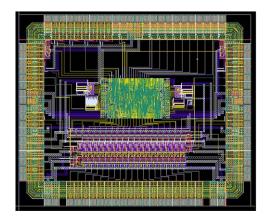

Fig. 3. Chip layout.

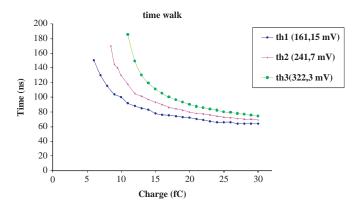

**Fig. 4.** Time walk vs Qin at  $C_{det} = 10 \, pF$ .

The GASTONE layout is reported in Fig. 3 for the developed prototype of 16 channels occupying a silicon area of  $3.2 \times 2.2 \text{ mm}^2$ .

A custom Front-End Board (FEB) has been developed, containing a protection circuit to protect the chip from possible spark chamber events [4] and housing two chips, for a total of 32 channels.

# 3. Test results

Measurements have been carried out both by means a test bench and with the electronics connected to the Layer 0 IT prototype in a dedicated test beam. Although data taking analysis is still in progress, preliminary results show the good uniformity response of the GASTONE chip over the detector area instrumented with it.

The chip has been tested on the test bench by using an Agilent Pulse Generator 81110A and a custom VME board where the SPI control and readout protocol has been implemented.

The measured ENC (erms) is about  $880\,\mathrm{e}^-+61\,\mathrm{e}^-/\mathrm{pF}$  corresponding to  $0.63\,\mathrm{fC}$  for an equivalent capacitance value of  $50\,\mathrm{pF}$  associated to the maximum strip length. This noise value sets a safe level of  $3\,\mathrm{fC}$  for the discriminated detector signal.

The time response of the chip as a function of the input charge has been measured for different thresholds and as expected by the adopted leading edge technique, it tends to increase as the charge

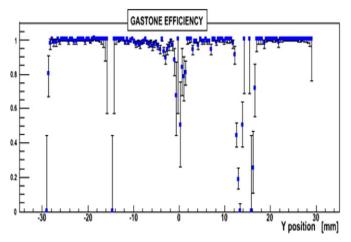

Fig. 5. GASTONE hit efficiency measurements.

approaches the discriminator threshold. In Fig. 4 the results for  $C_{\rm det} = 10 \, \rm pF$  are shown.

The hit efficiency has been measured and very preliminary results are shown in Fig. 5, where the impact point shape is due to the streamer tubes used as tracking system.

## 4. Conclusions

The test results demonstrated that GASTONE is suitable as readout electronics of the KLOE inner tracker detector. Its low noise and low power characteristic fully comply with the detector requirements. Some improvements are under development to integrate the protection circuit on the final 64-channel version of the chip, in order to increase the compactness of the final front end board that will host 128 channels.

# References

- KLOE-2 Collaboration: a proposal for the roll-in of the KLOE-2 detector, LNF, Frascati, Italy, March 31, 2006.

- [2] D. Moraes, et al., The CARIOCA front end chip for the LHCb muon chambers, LHCb-MUON 2003–2009.

- [3] J. Kaplon, et al., Fast CMOS binary front end for silicon strip detectors at LHC experiments, IEEE Trans. Nucl. Sci. NS52 (6) (2005).

- [4] E. Noschis, et al., Nucl. Instr. and Meth. A 572 (2007) 338.